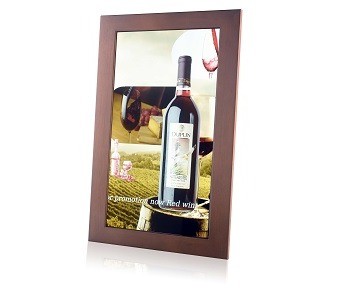

Display Monitor

FRS-D215EK-N0/6/7/8

The RSD190EK Series is IP69K-certified, ensuring superior protection against high-pressure and high-temperature washdowns.

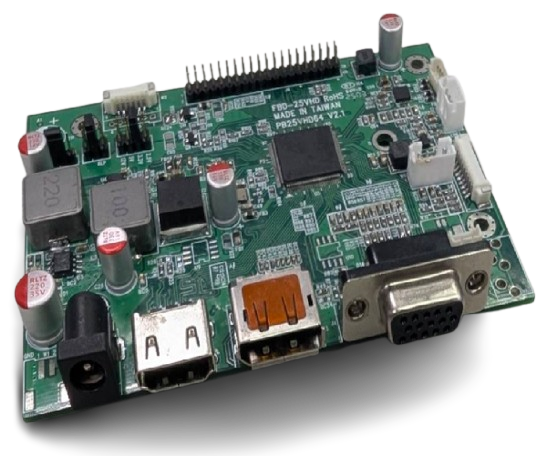

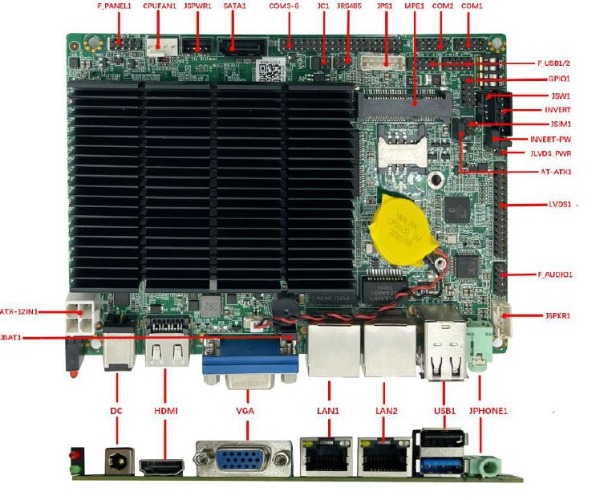

It supports multiple video input options, including DVI, VGA, HDMI, DP, and Type-C, providing flexible connectivity for various industrial applications.

Additionally, this series features PCAP multi-touch technology with an integrated touch power button, allowing users to disable touch functionality during cleaning to prevent accidental activation.

Because it has waterproof characteristics, it is suitable for use in places that need high hygienic and outdoor requirements. Such as:

1. Food & Beverage Industry

2. Pharmaceutical Industry

3. The Guide Of National Forest Park

4. Car Wash